Taking LEDs beyond lighting Pg 49

JUNE

Issue 11/2011

www.edn.com

What happens when software undermines hardware's potential? Pg 8

> Energy-efficient electronics Pg 16

Design Ideas Pg 41 Hammer it home Pg 52

#### VOICE OF THE ENGINEER

### PEERING INSIDE A PORTABLE, \$200 CANCER DETECTOR

Page 19

### DESIGNING IR Gesture-sensing **SYSTEMS**

Page 37

# EDA TOOLS Pave path to Page 26

DIGHTER WITTE PARTY OF TOUR HAND

## Hello future.

#### Goodbye status quo.

Oscilloscopes Redefined Starting at \$1,230\*

Agilent 2000 Tektronix Agilent 3000 Tektronix X-Series MS0/DP02000 **X-Series TDS2000C** (MSO and DSO) (MSO and DSO) Series (DSO) Series Bandwidth (MHz) 70, 100, 200 50, 70, 100, 200 100, 200, 350, 500 100, 200 Max sample rate 2 GSa/s 2 GSa/s 4 GSa/s 1 GSa/s Max memory depth 100 kpts 2.5 kpts 4 Mpts 1 Mpt Max update rate 50,000 200\*\* 1,000,000 5,000 (waveforms/sec) **Fully upgradable** Yes No Yes No **Function Generator** Yes No Yes No \*\*Refer to Agilent Pub 5989-7885EN for update rate measurements Data for competitive oscilloscopes from Tektronix publications 3GW-25645-0 and 3GW-22048-1 Notes: Measurements taken on same signal using Agilent MSOX2024A and Tektronix TDS2024B Screen images are actual screen captures and scopes are shown to scale

© 2011 Agilent Technologies, Inc. \*All prices are in USD and subject to change

> Agilent and our Distributor Network Right Instrument. Right Expertise. Delivered Right Now.

Buy from an Authorized Distributor www.agilent.com/find/distributors

See the difference today. www.agilent.com/find/redefined

### Digi-Key **TO THE INDUSTRY'S** LARGEST INVENTORY **Smartphone Applications**

YOUR PASSKEY

**OF IN-STOCK** ELECTRONIC COMPONENTS

Providing instant access for design engineers and purchasers to source the electronic components they need anytime, anywhere.

The industry's broadest product selection available for immediate delivery

Digi-Key is an authorized distributor for all supplier partners. New products added daily. © 2011 Digi-Key Corporation, 701 Brooks Ave. South, Thief River Falls, MN 56701, USA

f 🖻 🔠 📼 GET CONNECTED

# Find It Here, Faster.

The Newest Products for Your Newest Designs®

Authorized distributor for the most advanced semiconductors and electronic components.

Get What's Next. Right now at mouser.com.

Mouser and Mouser Electronics are registered trademarks of Mouser Electronics, Inc.

#### EDA tools pave the way to 3-D ICs

26 Going vertical enables higher-density circuits without scaling to smaller process geometries. by Mike Demler, Technical Editor

# EDN 6.9.11 contents

#### Peering inside a portable, \$200 cancer detector

**1** 9 Reducing health-care costs government, consumers, and corporations that buy health insurance. Toward that goal, Harvard University and Massachusetts General Hospital have developed a small, inexpensive cancer-detection device.

by Jim MacArthur, Electronic Instrument Design Laboratory, Harvard University

- 10 Easy-to-use benchtop source/ measure units provide wide voltage-versus-current ranges

- 12 MIT uses virus to increase solar-cell efficiency

- 13 New technology goes beyond OTP

- 13 KaiSemi claims automatic FPGA-to-ASIC conversion

- 14 Voices: NXP's Rick Clemmer: Bright lights, big opportunity

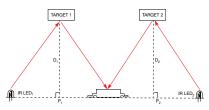

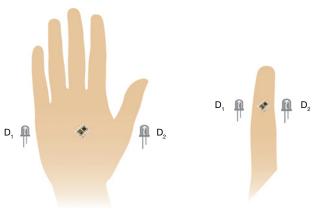

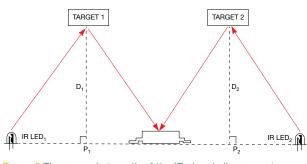

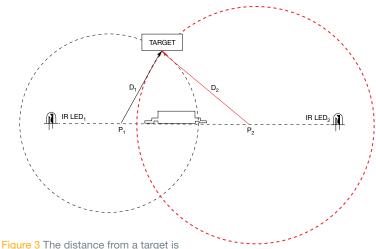

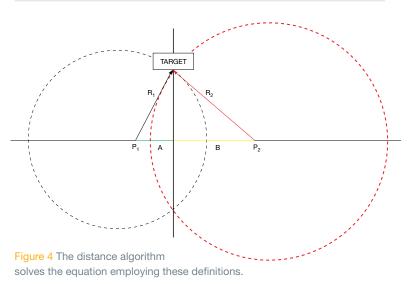

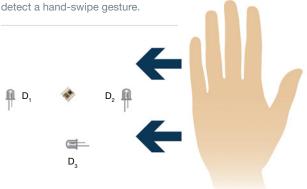

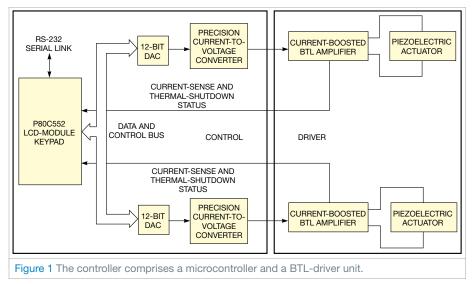

#### Designing IR gesture-sensing systems

37 Use or combine positionand phase-based sensing techniques to design accurate IR gesture-sensing systems.

by Alan Sy, Silicon Laboratories

#### COVER: ISTOCK

### DESIGNIDEAS

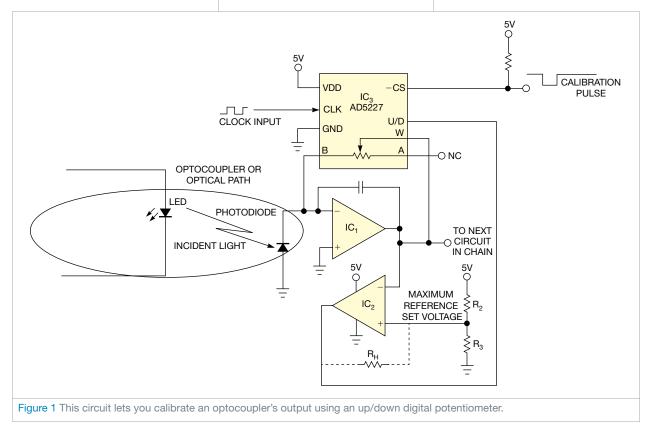

- 41 Potentiometer calibrates photodiode amplifier

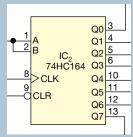

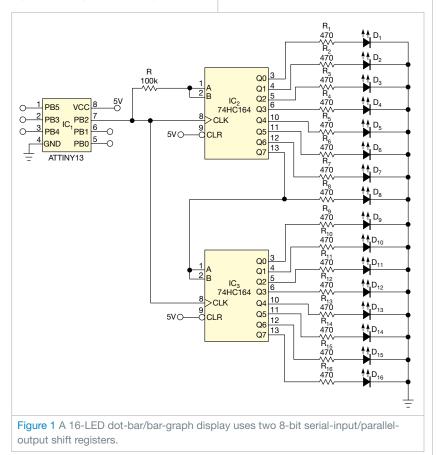

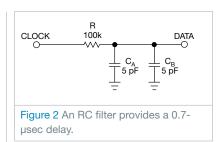

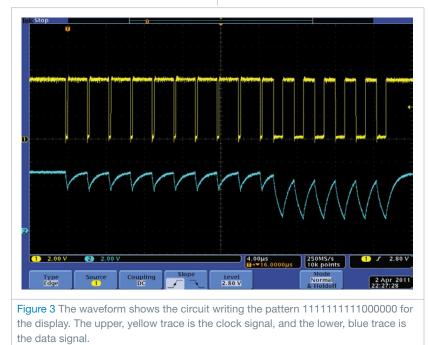

- 42 Drive 16 LEDs with one I/O line

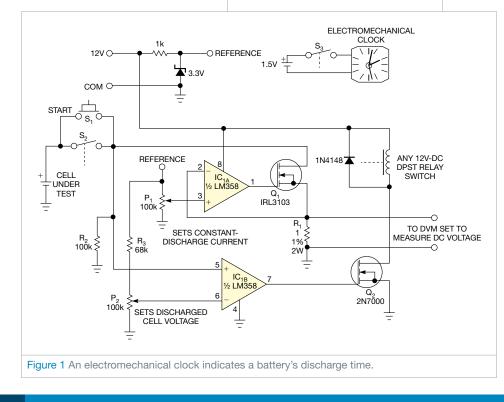

- 44 Circuit measures battery capacity

- 45 Programmable driver targets piezoelectric actuators

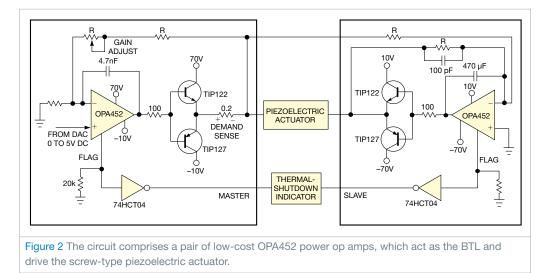

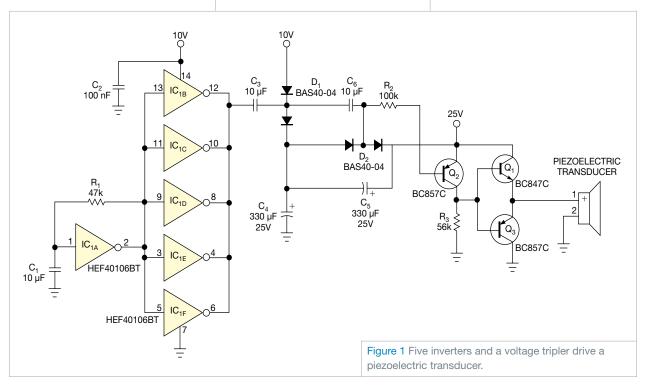

- 47 Circuit boosts voltage to piezoelectric transducers

# **Delivering Real Power**

#### Compact, Powerful CCM PFC from 75W to 4kW+

| PFC Control ICs |                                                                                          |  |

|-----------------|------------------------------------------------------------------------------------------|--|

| Part Number     | Description                                                                              |  |

| IR1152          | Fixed 66KHz switching frequency with brownout protection and dual OVP protection         |  |

| IR1153          | Fixed 22KHz switching frequency with brownout protection and programmable OVP protection |  |

| IR1155          | Programmable switching frequency and programmable OVP protection                         |  |

#### 600 V PFC IGBTs for High Power Systems I\_@ 100C V\_CE(on) (max) Circuit Package Part Number (V) (A) IRGB20B60PD1 22 2.35 TO-220AB IRGP20B60PD 22 2.35 TO-247AC Co-Pack IRGP35B60PD 35 2.15 T0-247AC IRCP50R60PD1 4 2 25 TO\_247AC

|          | 45       | 2.35                                       | 10-24/AC                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|----------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Discrete | 6.5      | 2.6                                        | TO-220AB; TO-220 FullPak                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|          | 12       | 2.7                                        | TO-220AB; TO-220 FullPak; TO-247AC                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|          | 20       | 2.5                                        | T0-262; T0-220AB; T0-247AC                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|          | 27       | 2.3                                        | T0-247AC                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|          | 35       | 1.85                                       | T0-247AC                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|          | 48       | 2.14                                       | T0-247AC                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|          | 90       | 2.1                                        | T0-247AC                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|          | Discrete | 6.5<br>12<br>20<br>Discrete 27<br>35<br>48 | 6.5         2.6           12         2.7           20         2.5           Discrete         27         2.3           35         1.85           48         2.14 | 6.5         2.6         TO-220AB; TO-220 FullPak           12         2.7         TO-220AB; TO-220 FullPak, TO-247AC           20         2.5         TO-262; TO-220AB; TO-247AC           21         2.7         TO-262; TO-220AB; TO-247AC           20         2.5         TO-262; TO-220AB; TO-247AC           20         2.5         TO-247AC           20         2.5         TO-247AC           35         1.85         TO-247AC           48         2.14         TO-247AC |

for more information call 1.800.981.8699 or visit us at www.irf.com

The µPFC family of controller ICs radically alters traditional thinking about PFC solutions. The IR115x uses a "One-Cycle Control integrator with reset" technique to deliver the high performance of Continuous Conduction Mode (CCM) PFC with the simplicity and low component count of Discontinuous Current Mode (DCM).

#### Features

- Small, easy, powerful solution

- Fast time to market

- Enables compliance with energy standards (1W, Blue Angel, Energy Star)

- No AC line voltage sense required

- 0.999 power factor

- Switching frequency of 22kHz, 66kHz or programmable value available

- · Average current mode control

- Cycle by cycle peak current limit system protection

#### International **ICR** Rectifier THE POWER MANAGEMENT LEADER

### contents 6.9.11

### **DEPARTMENTS & COLUMNS**

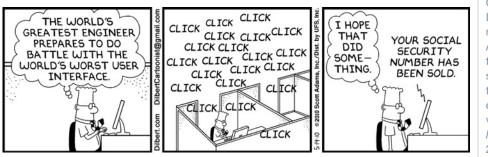

- 8 **EDN.comment:** What happens when software undermines hardware's potential?

- 16 Inside Nanotechnology: Energy-efficient electronics

- 49 Supply Chain: Light, life, and LEDs: taking LEDs beyond lighting

- 50 **Product Roundup:** Power Sources

- 52 Tales from the Cube: Hammer it home

#### **EDN** online contents

#### ONLINE ONLY

Check out these Web-exclusive articles:

#### High-speed differential signal conditioning makes reliable USB 3.0 systems

USB 3.0 design is closer to PCI Express than it is to USB 2.0. Here is how you make it work.

www.edn.com/110609toca

The Sony PlayStation 3 hack deciphered: what consumer-electronics designers can learn from the failure to protect a billion-dollar product ecosystem

A robust platform security system that begins with a clear set of security objectives is key to meeting the attacker challenge and surviving and recovering from similar onslaughts.

→www.edn.com/110609tocb

#### Securing the Internet of Things

Along with performance, efficiency, reliability, and cost, designers must now take security seriously.

→www.edn.com/110609tocc

#### PRYING EYES

In *EDN*'s Prying Eyes, we peer inside an end-user consumer gadget, a reference design, or any other interesting electronics-enabled thing we can get a good look at. Prying Eyes aims to illuminate the tough design decisions the engineers responsible for the design had to make. Find the entire Prying Eyes archive at www.edn.com/pryingeyes, or sample a couple of installments at the links below:

www.edn.com

The 15W Fender Squier guitar amplifier →www.edn.com/110609tocd

Remote phosphor expands reach of LED light

→wwww.edn.com/110609toce

EDN® (ISSN# 0012-7515) is published semimonthly by UBM Electronics, 600 Community Drive, Manhasset, NY 11030-3825. Pariodicals postage paid at Manhasset, NY, and at additional mailing offices. SUBSCRIPTIONS—Free to qualified subscribers as defined on the subscription card. Rates for nonqualified subscriptions, including all issues: US, \$150 one year; \$250 two years; \$300 three years. Except for special issues where price changes are indicated, single copies are available for \$10 US and \$15 foreign. For telephone inquiries regarding subscriptions, call 763-746-7292. E-mail: edn@omeda.com. CHANGE OF ADDRESS—Notices should be sent promptly to PO Box 47461, Plymouth, MN 55447. Please provide old mailing label as well as new address. Allow two months for change. NOTCE—Every precaution is taken to ensure accuracy of content; however, the publishers cannot accept responsibility for the correctness of the information supplied or advertised or for any opinion expressed herein. POSTMASTER—Send address changes to EDN, PO Box 47461, Plymouth, MN 55447. CANADA POST: Publications Mail Agreement 40612608. Return undeliverable Canadian addresses to BleuChip International, PO Box 25542, London, ON NEC 682. Copyright 2011 by United Business Media. All rights reserved. Reproduction in whole or part without written permission is prohibited. Volume 56, Number 11 (Printed in USA).

100-1000 VDC Output Hi-Efficiency/Excellent Load Regulation Single Output with Center Tap

Shown Actual Size

Input Over Voltage/Over Temperature Protection Remote Shutdown

- 100 to 1,000 VDC Outputs

- Input Voltage, 5V, 12V, 24V, 28V DC Standard

- Isolated Input to Output

- Ultra Miniature 0.55"x 0.75"x 0.4"

- Excellent Load Regulation

- Hi Reliability/Custom Models

- Military Upgrades/Environmental Screening Available

- Call Factory 800-431-1064

PICO Electronics,Inc. 143 Sparks Ave, Pelham, NY 10803-1837 E-Mail: info@picoelectronics.com

#### www.picoelectronics.com

**For Full Product Specifications**

MILITARY • COTS • INDUSTRIAL DC-DC CONVERTERS & POWER SUPPLIES TRANSFORMERS & INDUCTORS

#### BY BRIAN DIPERT, SENIOR TECHNICAL EDITOR

# What happens when software undermines hardware's potential?

n a recent article, I mentioned the RIM (Research in Motion) PlayBook (see "ARM versus Intel: a successful stratagem for RISC or grist for CISC's tricks?" *EDN*, April 7, 2011, pg 24, http://bit.ly/hQwGEu). I showcased it as one of the first announced design wins for Texas Instruments' OMAP (Open Multimedia Applications Platform) 4 SOC (system on chip). I also am well-acquainted with Motorola's Xoom tablet, which the company based on Nvidia's Tegra 2 dual-core SOC. Both the PlayBook and the Xoom have impressive hardware potential, but the currently available operating systems and application suites for both platforms sabotage that potential.

I have long felt that the PlayBook's dearth of support for native e-mail, calendaring, contacts, and similar applications—except through a Web-browser interface if the service provider offers that option—would constrain the device to being little more than a Palm Foleo-like device, dependent on a tethered handset. Don't forget that the Palm Foleo flopped.

RIM's primary market focus continues to be enterprises, in which the company's handsets are well-entrenched. Yet, RIM is also aggressively targeting consumers with its first tablet. The PlayBook's home-screen icons for Gmail, Facebook, and Twitter are currently nonfunctional placeholders. And those consumers who are AT&T subscribers, even if they have BlackBerry mobile phones, are completely out of luck: The cellular carrier's distaste for unsanctioned tethering has compelled it to reject the BlackBerry Bridge app, thereby blocking the tablet's access to a handset's e-mail, calendar, and contacts data.

Now consider the Xoom. Unlike its Android 2.x-based handset and tablet peers, the Android 3.x-based Xoom doesn't yet allow use of the microSD (secure-digital) slot for optional application installations, for file transfers, or even for users' data storage. The Motorola tablet's shortcomings extend beyond software to hardware. Although the company plans 4G (fourth-generation) LTE (long-term-evolution) cellular-data support, it is still shipping devices with 3G (third-generation)only transceivers. And, although the 4G upgrade will be free to Xoom owners, it will require that users do without the device for several days to several weeks while it undergoes upgrading at a Verizon or a Motorola service center.

Tablets aren't the only devices whose makers have neutered their features. For example, the Nintendo 3DS Web browser is not yet functional. These situations are especially baffling; it's one thing to omit a feature, but shipping a system with icons for-or other active references to-nonfunctional apps is especially insensitive to consumers. These systems' designers were perhaps uncomfortable with the decision to go to production with half-baked products, but upper management's desires to establish a market presence overrode the designers' concerns. In the case of the two tablets, company officials were attempting to slow the momentum of the Apple iPad. With the Nintendo 3DS, the twin motivations were to compete against smartphones and bolster a sagging corporate bottom line.

It's difficult to construct a case that early-production decisions for any of these devices were good ones. Earlyadopter buzz—either positive or negative—is a powerful phenomenon, and recovering from initial negative press, assuming that recovery is possible, requires substantially more time, money, and effort than does launching a more solid product in the first place.

The ship-it-early strategy sometimes pans out. Consider that the Xbox 360 hit the market a year before the Sony PlayStation 3 did, and, despite the Microsoft console's well-documented thermal issues, it flip-flopped the respective companies' market positions with the earlier-generation Xbox and PS2.

More often than not, though, a premature launch ends up playing out poorly for the supplier—and the ecosystem. Releasing software updates every two weeks, as RIM reportedly plans to do, is admittedly better than nothing at all, but it's not as good as waiting a few

#### Upper management's desires to establish a market presence overrode the designers' concerns.

months and providing a more robust feature foundation. It also subjects customers to periodic update hassles that they shouldn't have to bother with.

Updatable, nonvolatile code-storage devices, such as hard-disk drives and flash memory, enable upgradable software, which in turn fuels the temptation to launch early. The problem seems to have recently become worse, and I'm not sure what manufacturers can do to dodge the obstacles they keep hitting. What do you think?EDN

+ Read an expanded version of this column in the Brian's Brain blog at www.edn.com/110609eda.

ASSOCIATE PUBLISHER, EDN WORLDWIDE

Judy Hayes, 1-925-736-7617; judy.hayes@ubm.com

EDITORIAL DIRECTOR Ron Wilson, 1-415-947-6317; ron.wilson@ubm.com

MANAGING EDITOR Amy Norcross Contributed technical articles 1-781-869-7971; amy.norcross@ubm.com

MANAGING EDITOR—NEWS Suzanne Deffree Electronic Business, Distribution 1-631-266-3433; suzanne.deffree@ubm.com

SENIOR TECHNICAL EDITOR Brian Dipert Consumer Electronics, Multimedia, PCs, Mass Storage 1-916-548-1225; brian.dipert@ubm.com

TECHNICAL EDITOR Margery Conner Power Sources, Components, Green Engineering 1-805-461-8242; margery.conner@ubm.com

TECHNICAL EDITOR Mike Demler EDA, IC Design and Application 1-408-384-8336; mike.demler@ubm.com

> TECHNICAL EDITOR Paul Rako Analog, RF, PCB Design 1-408-745-1994; paul.rako@ubm.com

DESIGN IDEAS EDITOR Martin Rowe, Senior Technical Editor, Test & Measurement World edndesignideas@ubm.com

SENIOR ASSOCIATE EDITOR Frances T Granville, 1-781-869-7969; frances.granville@ubm.com

ASSOCIATE EDITOR Jessica MacNeil, 1-781-869-7983; jessica.macneil@ubm.com

CONSULTING EDITOR Jim Williams, Staff Scientist, Linear Technology edn.editor@ubm.com

#### CONTRIBUTING TECHNICAL EDITORS

Dan Strassberg, strassbergedn@att.net Nicholas Cravotta, editor@nicholascravotta.com Robert Cravotta, robert.cravotta@embeddedinsights.com

UBM Electronics COLUMNISTS

Howard Johnson, PhD, Signal Consulting Bonnie Baker, Texas Instruments Pallab Chatterjee, SiliconMap Kevin C Craig, PhD, Marquette University

VICE PRESIDENT/DESIGN DIRECTOR Gene Fedele

> CREATIVE DIRECTOR David Nicastro

> > ART DIRECTOR Giulia Fini-Gulotta

PRODUCTION Adeline Cannone, Production Manager Laura Alvino, Production Artist Yoshihide Hohokabe, Production Artist Diane Malone, Production Artist

> **EDN EUROPE** Graham Prophet, Editor, Reed Publishing gprophet@reedbusiness.fr

EDN ASIA Wai-Chun Chen, Group Publisher, Asia waichun.chen@ubm.com Kirtimaya Varma, Editor-in-Chief kirti.varma@ubm.com

EDN CHINA William Zhang, Publisher and Editorial Director william.zhang@ubm.com Jeff Lu, Executive Editor jeff.lu@ubm.com

EDN JAPAN Katsuya Watanabe, Publisher katsuya.watanabe@ubm.com Ken Amemoto, Editor-in-Chief ken.amemoto@ubm.com

> UBM ELECTRONICS MANAGEMENT TEAM Paul Miller,

Chief Executive Officer, **UBM Electronics** and UBM Canon (Publishing) Brent Pearson, Chief Information Officer David Blaza, Senior Vice President Karen Field, Senior Vice President, Content Jean-Marie Enjuto, Vice President, Finance Barbara Couchois, Vice President, Partner Services and Operations Felicia Hamerman, Vice President, Marketing Amandeep Sandhu, Director of Audience Engagement and Analytics

EDN. 33 Hayden Avenue, Lexington, MA 02421. www.edn.com. Subscription inquiries: 1-763-746-2792; EDN@omeda.com. Address changes: Send notice promptly to PO Box 47461, Plymouth, MN 55447. Please provide an old mailing label as well as your new address. Allow two months for the change. UBM Electronics, 600 Community Drive, Manhasset, NY 11030-3825. <text>

Dependability

<sup>66</sup>When they say they will deliver, I know I can depend on it. When you call Mill-Max customer service you get answers right away...<sup>99</sup>

Your product is only as good as each of its components. At **Mill-Max** we work hard to ensure that neither your product quality nor your schedule will ever be compromised.

<sup>66</sup> We've been ordering from Mill-Max for more than 12 years, and I can't remember ever having a rejected part...quality has been flawless.<sup>99</sup>

Our connectors speak for themselves...so do our customers.

To view our Design Guide, new product offerings and request a datasheet with free samples, visit www.mill-max.com/EDN610

# EDITED BY FRAN GRANVILLE STATE OF THE STATE

### Easy-to-use benchtop source/measure units provide wide voltage-versus-current ranges

gilent Technologies has announced the B2900A series, its first line of compact benchtop SMUs (source/measure units) for testing semiconductors, components, and materials. The units provide fast, simple current-versus-voltage characterization of semiconductors; active and passive components; and materials in research, development, manufacturing, and education. For example, the voltage range is ±210V, and current ranges are ±3A dc and ±10.5A pulsed. Sourcing is precise, and measurements are accurate with minimum resolution of 100 nV and 10 fA.

The intuitive GUI (graphical user interface) includes a 4.3-in. color LCD that supports graphical and numerical displays in single, dual, graph, and roll modes. By easing the quick completion of a variety of measurements and providing the ability to view the results on a color display, the B2900A series performs interactive testing, debugging, and characterization faster than do conventional SMUs.

In automated testing, the B2900A series units archive data at a maximum swept-operation reading rate from the sourced or measured quantity to the IEEE-488 bus of 12,500 readings/sec – twice the rate of competing SMUs. Under program control, the new SMUs support the SCPI (standard commands for programmable instruments) command set, providing Basic compatibility and enabling easy migration from conventional SMUs.

The B2900A series comprises the onechannel B2901A and B2911A and the twochannel B2902A and B2912A models. The B2901A and B2902A have current resolution of 100 fA; the B2911A and B2912A have current resolution of 10 fA. Capabilities such as the number of displayed digits, measurement resolution, minimum timing interval, and supported view modes further distinguish the instruments, making it easy to select a combination of price and performance that fits your testing needs.

It can be confusing to use conventional stand-alone instruments, such as voltage/ current sources and meters, switches, and arbitrary-waveform generators, to perform current/voltage measurements. An SMU integrates these capabilities in one compact instrument.

Many Agilent SMUs, including the B2900A series, can operate as four-quadrant voltage/ current sources,

Agilent B2912A Pre

+210.0000 V

+00.00001 nA

+10.50000 A

+06.00000

electrical loads, voltage/current meters, pulse generators, and arbitrarywaveform generators. These capabilities enable the instruments to

perform a variety of dc and low-frequency ac measurements without changing connections or using additional equipment. US list prices begin at \$5671.

—by Dan Strassberg ▶Agilent Technologies, www.agilent.com/find/B2900A. Although small, the B2912A performs a variety of benchtop current/ voltage-testing functions that would otherwise require many instruments and much greater setup time and cost.

####

"I wouldn't be too quick about blaming gear heads; a lot of really weak EEs out there simply do not understand the fundamentals of solder joints. And EEs do know everything."

-EDN reader "Andy T," in EDN's Talkback section, at http://bit.ly/ kXfx5u. Add your comments.

> 1 2 ABC 3 DEF 4 0H 5 ABC 6 MINO

7 PORS 8 TUV 9 WXYZ

4 1

0 +/\_

Windows<sup>®</sup> Life without Walls<sup>™</sup> Dell recommends Windows 7.

# Let your vision take shape.

### Unleash your creativity and imagine the possibilities. Then watch as they become reality with the power of Dell Precision<sup>™</sup> workstations and Autodesk<sup>®</sup> BIM software.

Dell Precision<sup>™</sup> workstations deliver the performance and graphics needed to run demanding applications with ease. Now your team can use data-rich modeling to evaluate new design options, predict building performance and communicate more productively.

- Blast through your workload faster than ever with the server-grade dual processor performance of a system powered by the Intel® Xeon® Processor 5600 Series. It's not just a workstation. It's an expert workbench.

- Genuine Windows® 7 Professional

- Scalable options select systems are available with up to 192GB of memory\* and 7.5TB of internal storage

- A full range of desktop, rack and mobile workstations to fit your needs

- ISV-certified for 95 leading applications, including Autodesk®

- Stay up and running with a 3-year Limited Hardware Warranty\* and optional 24/7 Dell ProSupport<sup>™</sup>

Find your ideal configuration online. Go to dell.com/smb/vision or call your sales rep at 1-888-927-3355.

\*Offers: Call: M-F 7:00a-9:00p Sat 8a-5p CT. \*Offers subject to change, may not be combinable with other offers. Taxes, shipping, handling and other fees extra and not subject to discount. U.S. Dell Small Business new purchases only. Limit : 5 discounted or promotional items per customer. Dell reserves the right to cancel orders arising from pricing or other errors. Graphics and system memory: GB means 1 billion bytes and TB equals 1 trillion bytes; significant system memory may be used to support graphics, depending on system memory size and other factors. Limited Hardware Warranty: For a copy of Dell's limited warranties write Dell USA L.P., Attn.: Warranties, One Dell Way, Round Rock, TX 78682. For more information, visit www.dell.com/warranty **Trademarks**: Celeron, Celeron Inside, Intel, Intel Logo, Intel LAtom, Intel Atom, Intel

Image provided by Autodesk and created with Au Revit software for building information

Powerful. Intelligent.

# pulse

# MIT uses virus to increase solar-cell efficiency

esearchers at the Massachusetts Institute of Technology claim to have increased the power-conversion efficiency of solar cells by nearly one-third through the use of tiny viruses to perform detailed assembly work at the microscopic level (Reference 1). The MIT researchers based their findings on the fact that carbon nanotubes can enhance the efficiency of electron collection from a solar cell's surface. They used a genetically engineered version of the M13 virus, which normally infects bacteria, to control the arrangement of the nanotubes on a surface. This approach keeps the tubes separate so that they can't short out the circuits and keeps the tubes apart so that they don't clump-two problems that have plaqued previous attempts to use carbon nanotubes in solar cells.

The system the researchers tested uses lightweight and inexpensive dye-sensitized solar cells, whose active layer comprises  $TiO_2$  (titanium dioxide), rather than the silicon that conventional solar cells use. The same techniques can be applied to quantum-dot and organic solar cells. In tests, adding the virus-built structures enhanced the power conversion efficiency to 10.6%

from 8%, almost a one-third improvement.

The researchers achieved this efficiency improvement even though the viruses and the nanotubes make up only 0.1% of the weight of the finished

cell. "A little biology goes a long way," says Angela Belcher, a WM Keck professor of energy who worked on the project. The researchers believe that they can even further ramp up the efficiency with additional work.

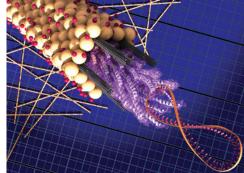

The M13 virus comprises a strand of DNA (deoxyribonucleic acid) attached to a bundle of peptides, which attach to the carbon nanotubes and hold them in place. A coating of TiO<sub>2</sub> attaches to dye molecules, surrounding

the bundle. The viruses improve one step in the process of converting sunlight to electricity: funneling electrons toward a collector, from which they can form a current that flows to charge a battery or power a device. Adding the carbon nanotubes to the cell provides a more direct path to the current collector, according to Belcher. The viruses possess peptides—short proteins that can bind tightly to the carbon nanotubes, holding them in place and separating them from each other. Each virus can hold five to 10 nanotubes; about 300 of the virus' peptide molecules hold each of these nanotubes firmly in place. The research-

The M13 virus comprises a strand of DNA (the figure-8 coil on the right) attached to a bundle of peptides (the corkscrew shapes in the center), which attach to the carbon nanotubes (gray cylinders) and hold them in place. A coating of titanium dioxide (yellow spheres) attaches to dye molecules (pink spheres), surrounding the bundle. More of the viruses with their coatings appear in the background (courtesy Matt Klug, Biomolecular Materials Group, MIT).

ers engineered the virus to produce a coating of  $TiO_2$ , a key ingredient for dye-sensitized solar cells, over each of the nanotubes. That step put the  $TiO_2$  in close proximity to the wirelike nanotubes that carry the electrons. The same virus performs the two functions in succession; the virus switches from one function to the next by changing the acidity of its environment. This switching feature is an important new capability that this research demonstrates for the first time. The viruses also make the nanotubes soluble in water, which makes it possible to incorporate the nanotubes in the solar cell using a

> water-based process that works at room temperature.

Japan, South Korea, and Taiwan have already commercialized dye-sensitized solar cells. Solar experts believe that the industry will adopt such processes if the addition of carbon nanotubes can improve their efficiency through the virus process. Because the process would just add one step to a standard solar-cell manufacturing process, it should be easy to adapt production facilities and should be possible to

implement relatively rapidly. Italian company Eni funded the research through MIT's Solar Futures Program.

-by Suzanne Deffree ▷Massachusetts Institute of Technology, www.mit.edu.

#### REFERENCE

Dang, Xiangnan; Hyunjung Yi; Moon-Ho Ham; Jifa Qi; Dong Soo Yun; Rebecca Ladewski; Michael S Strano; Paula T Hammond; and Angela M Belcher, "Virustemplated self-assembled single-walled carbon nanotubes for highly efficient electron collection in photovoltaic devices," *Nature Nanotechnology*, April 24, 2011, http://bit.ly/IJysWi.

#### **DILBERT By Scott Adams**

# New technology goes beyond OTP

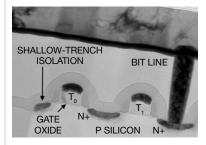

ilicon-IP (intellectualproperty) vendor Kilopass Technology has added multitime programmability to antifuse-based nonvolatile memory. An antifuse-based memory can be programmed by breaking down a silicon-oxide barrier to set the state of the memory bit in a twotransistor cell. Like a ROM, programming with antifuse memory has traditionally been an OTP (one-time-programmable) process. With the announcement of Itera technology, Kilopass adds multitime programmability of as many as 1024 cycles for memories with as much as

1 Mbit of storage capacity. The company targets applications in software protocol stacks for wireless applications in Wi-Fi and Bluetooth, low-frequency data logging, and SOCs (systems on chips) that require periodic software updates.

Antifuse memory is smaller and offers less programmability than flash memory, but the Kilopass technology allows you to manufacture in a standard CMOS-logic process and scale it to 28 nm and smaller processes without any additional process steps. The result is lower manufacturing cost for trimming analog blocks, storing small amounts of code, and verifying security identification. Access time is 20 nsec in the 40-nm version of Itera. For larger capacity requirements, the Kilopass Gusto memory IP, which the company introduced in 2010, offers as much as 4 Mbits of nonvolatile OTP memory.

Kilopass offers Itera with a per-design license fee for the use of Itera or as a per-wafer royalty. Designers can then use Itera for applications with requirements of 32 bits to 1 Mbit. It is available now for manufacturing at foundries, including TSMC (Taiwan Semiconductor Manufacturing Co, www.tsmc. com), GlobalFoundries (www. globalfoundries.com), and UMC (United Microelectronics Corp, www.umc.com), in 40-nm bulk

The Kilopass memory IP provides one-time or multitime programmability with a two-transistor antifuse cell for manufacturing nonvolatile memory in standard CMOSlogic processes.

silicon. Kilopass also plans to make Itera available in 65- and 55-nm processes this year.

-by Mike Demler ►Kilopass Technology, www.kilopass.com.

00.00

#### KaiSemi claims automatic FPGA-to-ASIC conversion

Using a variety of processes from 90 to 500 nm, fabless semiconductor vendor KaiSemi Ltd recently unveiled automated conversion, a process to convert most current FPGA designs to drop-in ASIC replacements. According to Tomer Kabakov, the company's vice president of marketing, the flow begins with a design review. The customer provides a frozen FPGA netlist and an SDF (standard-delay-format) file; functional test vectors; pin definitions, including electrical requirements; and a checklist of additional information, such as timing constraints, clock frequencies, and test strategy. Kabakov notes that strong indicators of the convertibility of a netlist are the successful operation of the design in production and the completeness of the test-vector set. Beyond that, the review looks for known conversion obstacles, such as asynchronous blocks or multigigabit I/Os.

KaiSemi then runs its conversion tool. A run takes 12 to 24 hours, depending on the original design's size. The tool transforms the FPGA netlist into a cell-based ASIC netlist using a proprietary set of libraries that KaiSemi developed for the purpose. This process is not a simple mapping of look-up tables, multiplexers, and registers into cells, Kabakov says. The tool infers logic functions from the FPGA netlist and attempts to map them into functional blocks from the libraries. KaiSemi also attempts to map third-party IP (intellectual-property) blocks directly rather than through netlist conversion.

The approach should not only produce better results for a random-logic netlist but also address two problems in conversion: block RAM and DSP blocks. The tool examines the configuration of block RAM and its wrapper in the FPGA netlist, infers the actual RAM function the design uses—a small multiport, say, or a large FIFO (first-in/first-out) buffer with overflow and underflow flags—and instantiates the correct function in the ASIC netlist. It does not attempt to replicate the block RAM itself.

Similarly, the tool examines the netlist's use of FPGA DSP blocks and infers an optimized datapath. The cellbased netlist in KaiSemi's older processes can usually keep up with the maximum clock rate the customer is applying to the nominally faster DSP block in the FPGA.

The flow moves from translation to formal and functional netlist verification and from there to a conventional ASIC back-end flow: scan/test insertion, resimulation, and physical design. By translating netlists rather than resynthesizing RTL (register-transfer-level) logic, KaiSemi stays closer to the original design and substantially shortens the front-end-design time. By inferring intent from the netlist, however, the tool escapes slavishly duplicating the FPGA-specific fine structure of look-up tables, registers, and hard-function blocks.

KaiSemi charges no NRE (nonrecurring-engineering) costs for the conversion service. The vendor calculates the unit price for the resulting ASIC based on the complexity of the design, the manufacturing cost, and the amortization of the cost conversion.—by Ron Wilson KaiSemi, www.kaisemi.com.

# pulse

### VOICES

#### NXP's Rick Clemmer: bright lights, big opportunity

Rick Clemmer, executive director, president, and chief executive officer of NXP Semiconductors, recently talked with *EDN*, discussing speculation on NXP's future, reviewing the company's most recent quarter and capacity shifts, and revealing how NXP's NFC (near-field-communication) strategy is allowing the company to shine with major lighting-application moves, including its GreenChip smart-lighting product, which NXP calls an "Internet address for every light bulb," and its intent to make its JenNet-IP (Internet Protocol) ultra-low-power, IEEE 802.15.4based wireless-connectivity network-layer software available under an open-source license. The following is an excerpt of that interview. You can read the full interview at www.edn.com/110609pa.

#### NXP's first-quarter product revenue from continuing operations of \$979 million was up 4.4% sequentially, and net profit was \$187 million. How did you accomplish this growth?

Some of the things that contributed to that [growth] were that, for our ID [identification] business, which has been capacity-limited, we were able to pull forward some of the increased manufacturing capacity we were bringing online. It allowed us to really drive increased growth. We had set expectations to be roughly flat, and we were able to achieve a 4.4% sequential growth. Most of our peer group was negative in that quarter because of its inherent cyclic [nature].

#### How is NXP's cost-savings effort, the Redesign Program, going?

We're most of the way through the Redesign Program. We've said that we will achieve \$900 million to \$950 million in savings. Through the end of last quarter, we were at [approximately] \$811 million or so. We have \$100 million plus to go, but we are basically on track. It's just about executing that [goal]. There's not a lot of additional increase to come.

NXP's recently announced GreenChip smart lighting screams "Internet of Things." What's your take on the phenomenon, and how does the Internetaddress-for-every-light-bulb initiative fit in?

When [Google Executive Chairman] Eric Schmidt talked about Web 2.0, he talked about NFC and the convenience it would bring to users. Clearly, the technology we provide [will] facilitate that [convenience] and ... make [it] work for Google and for everyone else. The [GreenChip smart-lighting action] takes us away from the Internet of people to the Internet of Thingsthe ability to control things, whether it's lighting, home appliances, white goods, or

security cameras. It's the ability to have that control and have a significant impact on energy consumption. [Approximately] 25% of home-energy consumption is in the form of lighting, and at least 30% of that energy consumption is wasted because it is in the form of heat as opposed to lighting itself. By us providing this capability, it allows someone to address that [consumption] so that they can have significant energy savings.

We are also announcing the opening of our software stacks, similar to what we did with NFC. Applications associated with NFC [are] limited only by the imagination of the application developers. Opening the software stacks on the "smarter home" gives us the ability to drive those same kinds of inherent accelerations on energy-cost savings. We think there is a clear opportunity for governments to participate in this [technology], but, even without their participation, the deployment costs associated with [this move for users] can be paid back in roughly a half-year. It offers the opportunity to significantly reduce overall energy consumption; it's in line with what governments have prioritized for reducing carbondioxide emissions and energy requirements. And we think that the ability to facilitate and drive that [idea] with strong partnerships with GreenWave

and TCP allows us to establish the proof in our ability to drive what we think is a unique and exciting technology.

### Will lighting be as big a market for NXP as NFC is?

When we look at the total market, it's different. I think it can be bigger than NFC, potentially. When we look at the combination of what we've called the smart connected network, which includes the automation of white goods and e-metering as well as lighting automation, we think that the market for semiconductors can be about \$4.5 billion by 2015, and roughly a fourth to a third of that [amount] will be associated with lighting and lighting automation. So there's a significant amount that will take place even without [lighting].

There's a lot going on with NFC. ZTE, for one, is using NXP's NFC. Visa last month unveiled its entry into "digital wallets." And Apple and Google have stated interest. How's the competitive outlook from your standpoint?

A lot of people are start-🐴 ing to talk about it. We've said that, when 30 or 40% of handsets have NFC in them, then it will be integrated into the connectivity chip. We fully expect at some point that the radio portion itself will get integrated. We are trying to ensure that we are focused on the total solution and that the total solution includes a combination of the secure element, the radio, as well as the software. When the radio gets integrated, we want to be sure that we are providing the secure element for hundreds of millions of units associated with it. - interview conducted and edited by Suzanne Deffree

#### AT THE FRONTIERS OF SIMULATION

# CST STUDIO SUITE 2011

# Explore the EM simulation universe

Crosstalk analysis www.cst.com/pcb

→ Get equipped with leading edge EM technology. CST's tools enable you to characterize, design and optimize electromagnetic devices all before going into the lab or measurement chamber. This can help save substantial costs especially for new or cutting edge products, and also reduce design risk and improve overall performance and profitability.

Involved in signal or power integrity analysis? You can read about how CST technology was used to simulate and optimize a digital multilayer PCB's performance at www.cst.com/pcb. If you're more interested in EMC/EMI, we've a wide range of worked application examples live on our website at www.cst.com/emc. Now even more choice for SI/PI simulation. The extensive range of tools integrated in CST STUDIO SUITE enables numerous applications to be analyzed without leaving the familiar CST design environment. This complete technology approach enables unprecedented simulation reliability and additional security through cross verification.

$\rightarrow$  Grab the latest in simulation technology. Choose the accuracy and speed offered by CST STUDIO SUITE.

CHANGING THE STANDARDS

### INSIDE NANOTECHNOLOGY

#### BY PALLAB CHATTERJEE, CONTRIBUTING TECHNICAL EDITOR

#### **Energy-efficient electronics**

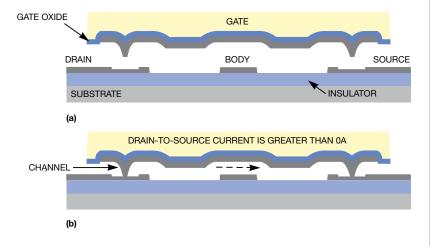

ou can optimize many aspects of nanoelectronics and MEMS (microelectromechanical-system) technology. The University of California—Berkeley has an ongoing research program that focuses on creating approaches to making energy-efficient circuits and devices. The program covers materials, magnetics, photonics, MEMS devices, circuit designs, and modeling.

Researchers in the photonics realm are working on developing smaller vertical- and lateral-facing LED-laser sources for short-range interconnect. One of the goals of developing these high-speed circuits is to as quickly as possible transfer information to the adjacent chips. However, sending the information in a traditional electrical current or voltage fashion generates and wastes heat. Further, physical-process variation affects resistance and capacitance for minimum delay. The new devices are targeting LED photonics, including light sources, light-steering methods, and detectors. The research is on the fundamental level from materials and process-flow technologies. These new devices are targeting a tenfold improvement over current energy levels as their operating goal.

Similarly, researchers are considering new device architectures. For example, one of the researchers, Tsu-Jae King Liu, PhD, has been looking at MEMS that manufacturers can make reliably using standard processing and that can find use in new applications at a lower power. One of the greatest sources of power and current loss is leakage in the off state of

a transistor acting as a switch. Liu and her team have been working on circuits based on electrostatic MEMS devices that have 0A off-state current. **Figure 1** shows the cross sections for the off and on states of a four-transistor relay circuit. This device has a physical air gap between the two states; as a result, the device has high off-state resistance. When the device makes a connection, it has a relatively low on-resistance.

This sort of device is useful for both logic functions with ultralow-steadystate power draw and for switched-power-rail applications on standard nanoelectronics circuits. The researchers created the devices using atomic-layer deposition and tested them in the lab. The devices exhibit a 100-nsec switching time for a less-than-2V gate-switch control voltage. The devices show no detectable wear even after the preliminary testing of 1 billion on/off cycles.

Eli Yablonovitch, PhD, heads the program. Yablonovitch also heads a basic materials program. His team is researching some magnetic and electromagnetic materials with a combination of elements. The team is reviewing these materials both for their standard memory capacities for nonvolatile and 3-D stacked-memory elements and for active devices. The researchers are targeting these materials for the practical realization of those technologies and others. Researchers are also studying the materials to see whether they can improve traditional rotating storage media, such as disk drives.

On the active-response side, researchers are using these materials for near-OV power logic that can also support circuitry to help sense, amplify, and distribute the data in the devices. The use of these materials is for direct applicability on traditional CMOS processes, on the silicon-interposer technology for 3-D stacked devices, and as stand-alone MEMS-wafer processes.

All of these technologies will drive change for the industry and its quest for a more-than-tenfold reduction in power in the next five years. EDN

Pallab Chatterjee is on the IEEE Nanotechnology Council.

### Data acquisition just got a lot easier.

#### More ways to control. More ways to connect.

The new Agilent 34972A Data Acquisition Switch Unit takes our best-selling Agilent 34970A to the next level. For starters, you get convenient built-in LAN and USB connectivity. Plus, you can control your data acquisition remotely via Web interface. And transfer logged data to your PC with a simple flash drive. No more expensive adapters and connectors. That's easy. That's Agilent.

| NEW 34972A                                                                    | 34970A                                             |  |  |

|-------------------------------------------------------------------------------|----------------------------------------------------|--|--|

| USB and LAN                                                                   | GPIB and RS232                                     |  |  |

| Graphical web interface<br>Benchlink data logger software<br>SCPI programming | Benchlink data logger software<br>SCPI programming |  |  |

| 3-slot LXI unit with b                                                        | 3-slot LXI unit with built-in 6 ½ digit DMM        |  |  |

| \$1,845                                                                       | \$1,597*                                           |  |  |

© 2010 Agilent Technologies, Inc. \*Prices are in USD and are subject to change.

Agilent and our Distributor Network Right Instrument. Right Expertise. Delivered Right Now.

Learn how to connect wirelessly and get more FREE measurement tips at www.metrictest.com/agilent/daq.jsp

At Molex, we know that the best ideas come from collaboration. From sharing insights and tackling tough challenges together. That's why we use our interconnect expertise to partner with our customers. Because when we support their innovations, we help the world move forward.

Get inspired. molex.com

## INNOVATORS INSPIRING INNOVATORS

📑 💽 🔝 🔠 💽 Join the conversation at:

## PEERING INSIDE A PORTABLE, \$200 CANCER DETECTOR

REDUCING HEALTH-CARE COSTS IS A KEY CONCERN FOR THE US GOVERNMENT, CONSUMERS, AND CORPORATIONS THAT BUY HEALTH INSURANCE. TOWARD THAT GOAL, HARVARD UNIVERSITY AND MASSACHUSETTS GENERAL HOSPITAL HAVE DEVELOPED A SMALL, INEXPENSIVE CANCER-DETECTION DEVICE.

#### BY JIM MACARTHUR • ELECTRONIC INSTRUMENT DESIGN LABORATORY, HARVARD UNIVERSITY

s part of a project to design the electronics for a portable, low-cost cancer detector, I had to understand NMR (nuclear magnetic resonance), a measurement technique that excites and measures the spin precessions of atomic nuclei. I also relied on the expertise of Hakho Lee, PhD, and David Issadore, PhD, two researchers at Massachusetts General Hospital's Center for Systems Biology. Lee

had been using magnetic-relaxation switching to explore ways to reduce the size and bulk of an NMR machine to the point at which it could be carried into the field to perform medical diagnostics.

Lee had refined an NMR-based technique for detecting tuberculosisspecific proteins, using a fist-sized permanent magnet and a rack full of electronics. My task was to squeeze that rack into a book-sized unit. The electronics box needed to create a string of RF pulses of precisely controlled frequency in the range of 20 to 30 MHz, and the phase between the first and subsequent pulses also had to change by a precisely controlled amount. This discussion requires some background on NMR techniques.

#### **NMR 101**

"NMR" refers to any of several measurement techniques that excite and measure the spin precessions of atomic nuclei. Think of a proton as a sphere with its charge uniformly distributed throughout. The proton's spin can be understood as making it rotate at a fixed rate. This rotation makes every bit of charge move in a circle. Then, analogous to current in a solenoid, these moving charges create a magnetic field, or "moment," that aligns on the spin axis. As with a macroscopic magnet, this magnetic moment tends to align with an externally applied magnetic field.

Just as perturbing a gyroscope makes it precess around the axis of the external gravitational field, perturbing a proton with a burst of RF (radio-frequency) energy at a certain frequency in the presence of a magnetic field makes its moment precess at the same frequency. This resonant frequency, the Larmor frequency, is a function of the magneticfield strength in the proton's neighborhood. Irish physicist and mathematician Joseph Larmor in 1896 proposed the Larmor frequency, which stipulates that a magnetic moment in a magnetic field tends to align with that field. As the proton's magnetic moment gradually realigns with the external magnetic field, the proton emits RF energy, again at its Larmor frequency.

Not only protons but also many atomic nuclei—those possessing an odd number of protons or neutrons—have spin, with different Larmor frequencies. Hydrogen's frequency, for example, is 42.58 MHz/tesla. One tesla equals 10,000 gauss; one gauss is approximately equal to the earth's magnetic-field strength. Nitrogen's frequency is 3.09 MHz/tesla. Conversely, the common isotopes of oxygen and carbon have no net spin; therefore, NMR cannot detect them.

In NMR spectroscopy, each element has a unique frequency, and nearby atoms slightly shift a given atom's Larmor frequency, making it possible to infer the molecular structure of a sample (**Reference 1**). NMR spectroscopy's success depends on correctly interpreting tiny changes in Larmor frequencies, which themselves are functions of the surrounding magnetic field. As such, the technique requires care in creating a uniform and stable magnetic field.

In addition to determining a proton's Larmor frequency, the RF signal also provides the two time constants of the decay in spin precession. After

#### AT A GLANCE

Each element has a unique Larmor frequency, and nearby atoms slightly shift a given atom's frequency. The combination of these two actions makes it possible to infer the molecular structure of a sample using NMR (nuclear-magnetic-resonance) spectroscopy.

Include no more than one new concept per subsystem because fixing two bugs is an order of magnitude harder than fixing one.

Maintaining documentation discipline is difficult when you are trying to meet deadlines; design reuse without a document trail, on the other hand, is practically impossible.

A digital camera with a macro lens is a useful tool for documenting hardware changes.

The biggest barrier to using an FPGA approach may be software. If some new IP (intellectual-property) core doesn't work as its manufacturer advertised or some new software revision makes your board stop working, you are at the mercy of technical support.

a proton is perturbed, it relaxes to bulk thermal equilibrium with a time constant of  $T_1$ . Interaction with neighboring

spins causes a shorter time constant, T<sub>2</sub>. These interactions detune the individual precessions, causing destructive interference and shortening the decay time.

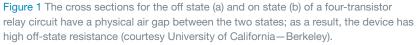

T<sub>2</sub> describes the immediate magnetic environment of each nucleus and, thus, its molecular composition;  $T_{\gamma}$ also provides information about the inhomogeneity of the bulk magnetic field. The greater the inhomogeneity, the more the individual Larmor frequencies will interfere and the faster the RF signal will decay. In all but the most carefully controlled magnetic fields, the bulk field's inhomogeneity effects completely overwhelm the more interesting information about a proton's immediate neighborhood. You can solve this problem using spin echo, an elegant technique, which works as follows.

Start by sending an RF pulse with enough energy to bring the precession angle of the magnetic moments down to 90° with respect to the bulk magnetic field. At first, the precessions are all in phase with each other, with emitted RF at a maximum. Nearly immediately, however, the Larmor frequencies cause the precessions to dephase. After a few milliseconds, the dephasing reaches its maximum, and the net radiated RF is consequently low.

Next, send another RF pulse that is twice as long as the original. Because

Figure 1 By plotting the decay of the peaks of the echoes, you can get an accurate assessment of T<sub>2</sub>. Times are approximate and adjustable.

the first pulse rotates each magnetic moment by 90°, the second pulse rotates it 180° more. To picture what happens next, imagine holding a closed paper fan before your face and then slowly opening it to represent the dephasing process. The righthand part of the fan represents the faster moments, and the lefthand part represents the slower moments. Now, flip the fan around. The faster moments are now on the left; they begin catching up with the slower moments, closing up the fan and restoring the RF signal.

You can repeat this process until the precessions completely decay (**Figure 1**). By plotting the decay of the peaks of the echoes, you can get an accurate assessment of T<sub>2</sub>.

This article provides only a cursory treatment of NMR, using classic analogies to describe an inherently quantum effect. However, my goal was to provide a taste of the engineering issues. Most of the Larmor frequencies of interest are in the decade between 10 and 100 MHz, which, from an engineering standpoint, is a good place to be because lots of earlier RF-design concepts are applicable. Although the design of the receiver chain isn't trivial, for example, it's a piece of cake compared with tuning in and identifying short-wave radio signals from thousands of miles away.

The SNR (signal-to-noise ratio) increases with the static magnetic field, so keep the field as high as possible. For large samples, this means using a massive magnet with supercooled coils. For small samples, on the other hand, you can create fields larger than 1 tesla with a handheld permanent magnet. The small magnet in the DMR-3, the official name for this instrument, creates a roughly 0.5-tesla field (Figure 2). Relaxation times are on the order of a few milliseconds to a few seconds. Demodulated signals range to tens of kilohertz; you must acquire data at 100 kHz, for example, for a second or so. This is not, in other words, a taxing data-acquisition problem.

#### **IDENTIFYING THE PROBLEM**

While I was working on this project, Lee and Issadore were working on their goal of making the NMR portable. In pursuit of this goal, Lee used magneticrelaxation switching, which binds magnetic nanoparticles to proteins by first binding the nanoparticles to protein-specific antibodies, which in turn bind to proteins. Once these nanoparticles find the target proteins, they clump together, significantly decreasing the spin-relaxation time of nearby atoms. In other words, clumped nanoparticles translate to a shorter  $T_2$ .

returned signal at the RF frequency and then digitize it at 100,000 samples/sec for several seconds. Several stacked runs' results would be transmitted to a host computer for analysis. All pulse timing needed to be accurate to 1 µsec or better. The host computer controls all parameters over USB (Universal Serial Bus)and asynchronous-interface ports. The box had to be rugged and portable, and

My design needed to demodulate the

www.isipkg.com 805.482.2870 info@isipkg.com

Figure 2 The DMR-3 uses a smartphone as a display.

the first deployment would be in Africa (references 2 and 3) in three months.

#### **DESIGNING THE SYSTEM**

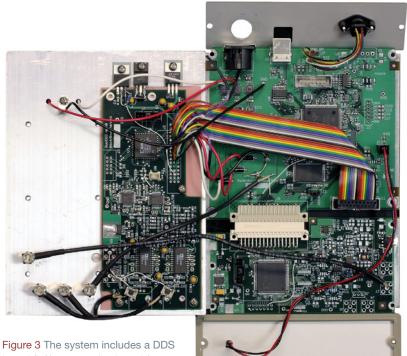

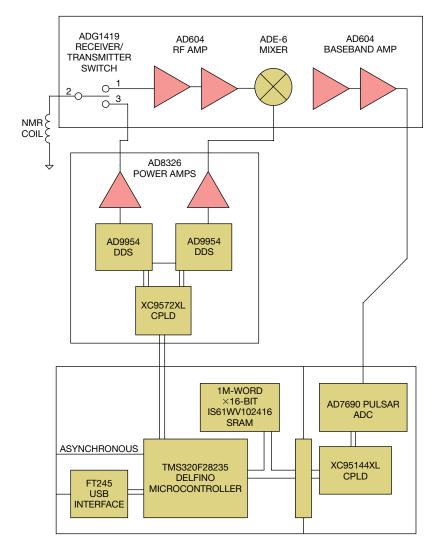

The package for the system is a Lansing Instrument MicroPak enclosure. The top cover is replaced by a custom-milled piece of aluminum, doing double duty as a heat sink for the RF transmitter and a quiet enclosure for the RF-receiver chain. The instrument contains four PCBs (Figure 3). The controller, ADC, and DDS (direct-digital-synthesizer) boards live in the bottom section, and the new board containing the RF-receiver signal chain is up top (Figure 4). The controller board includes a Texas Instruments TMS320F28235 Delfino DSC (digitalsignal controller), an ISSI (Integrated Silicon Solution Inc) IS61WV102416 asynchronous 1M-word×16-bit SRAM, and an FTDI (Future Technology Devices International) FT245 USBinterface chip.

The Delfino DSC performs speedy, 32-bit math and I/O operations, and it comes with an array of peripherals perfect for instrumentation, including highresolution PWMs (pulse-width modulators) and time stampers, UARTs (universal asynchronous receivers/transmitters), CAN (controller-area-network) circuitry, and DMA (direct-memoryaccess) controllers. Most important, it features full silicon support for runtime debugging—not just for setting breakpoints but also for viewing, altering, and logging memory and register space when the processor is running at full speed.

I considered using an FPGA but decided against it. Although the cost of materials doesn't strongly drive my design decisions, I can't justify replacing a \$25 microcontroller with a \$250 FPGA. And the BGA packaging typical of FPGAs is an issue for small production runs. The biggest barrier to using an FPGA approach, however, is software. Every FPGA developer I know has a horror story of some new IP (intellectual-property) core that didn't work as advertised or how some new software revision made a board stop working.

That said, I do scatter small FPGAs and CPLDs (complex programmablelogic devices) throughout my designs as insurance against mistakes and to allow for reuse in unanticipated ways; the DMR-3 contains two of them, for example. As a side benefit, programmable logic can often unscramble buses and do other board-cleanup chores, turning a risky six-layer PCB design into a simpler four-layer configuration. The Delfino DSC talks to the DDS board via a clocked serial protocol implemented with GPIO (general-purpose input/ output) pins. The DDS board contains a pair of synchronized Analog Devices AD9954 DDS chips, which generate RF signals at the same frequency, but with programmable phase separation. One DDS chip generates the NMR transmitted signal; the other creates the local oscillator that mixes the received signal to baseband.

The AD9954 is admittedly something of an odd choice. Alternatively, I could have used a dual-DDS AD9958 chip, which I already had because I'd used it for a physics experiment that required eight phase-staggered sine waves slowly swept from 10 kHz to 20 MHz. This problem is a nasty one in the analog domain, but it's not so bad with a bunch of DDS chips. From them, a pair of now-obsolete AD8326 CATV (cable-television) amplifiers amplify the RF signals, illustrating the point that baseband amplifiers, which get faster every year, can process RF signals in the 10- to 100-MHz range. A search on the Web for "CATV" and "DSL" (digital-subscriber-line) produces lots of useful amplifiers that work into the tens of megahertz.

From the DDS board, the NMR's transmitter and local-oscillator signals transfer through the aluminum top block and into the RF cavity, containing the only new board in the system. For this design, I stayed with the receiver-signal chain that Lee had tested: a pair

board (left), a controller board (top right), and an ADC board (bottom

right). Because the DDS and power-amplifier chips get hot and because supplemental ventilation is impossible, the DDS board mounts on the top-cover heat sink with Bergquist foam.

Figure 4 In the RF section of the design, the trimming potentiometers control the gains of the AD604 amplifiers.

of dual variable-gain AD604 amplifier chips, with a Mini-Circuits ADE-6 mixer between them. For the receiver/ transmitter switch, I chose an ADG1419 IC, which lacks the isolation of a more traditional RF switch but comes in a more convenient package. I solved the isolation problem by turning off the transmitter signal at the DDS board.

The demodulated, amplified signal returns to the noisy part of the box, where it is digitized by an Analog Devices AD7690 PulSAR (successiveapproximation-register) ADC sampling as fast as 100,000 samples/sec (Figure 5). This pin-compatible series of converters lets me select an optimal speed and SNR for my application without changing the PCB's design. The ADC board also

#### FOR MORE INFORMATION

Analog Devices www.analog.com

Apple Computer www.apple.com

Bergquist www.bergquist company.com

FTDI www.ftdichip.com

Harvard University www.harvard.edu

ISSI www.issi.com

Lansing Instrument Corp www.lansingenclosures.com Biology http://csb.mgh. harvard.edu MathWorks www.mathworks.com Mini-Circuits www.minicircuits.com National Instruments www.ni.com Texas Instruments

Massachusetts

General Hospital

**Center for Systems**

Texas Instruments www.ti.com Xilinx

www.xilinx.com

contains a Xilinx XC95144XL CPLD to handle housekeeping and serial/parallelconversion tasks, as well as to interface to DACs I didn't use for the design. Alternatively, I could have interfaced the ADC directly to the DSC through its McBSP (multichannel buffered serial port), but the ADC board was at hand.

The ADC board interfaces to the controller board through a 48-pin DIN connector containing the DSC's 16-bit data bus along with a few address and strobe lines. The DSC uses DMA to transfer one 262,144-sample NMR scan of ADC data into the external SRAM. Between scans, it adds the data from the last scan to another area of external SRAM that stores the accumulated scans. When the host decides that the instrument has accumulated enough scans, it reads out the accumulated data over the USB interface.

Note that USB is not an isolated protocol. As soon as you plug in a USB cable, you've connected your instrument's ground to your PC's ground, with predictable results. It's therefore a good idea to consider adding isolation, or be ready to specify an external isolator. Also, the FT245 chip that I used for the USB interface has a virtual-communication port that dramatically simplifies the host software's burden, allowing control through MathWorks' Matlab and National Instruments' LabView, for example. A trade-off exists, however, in that the host periodically sends packets to the USB to poll the status of the instrument's USB chip. In sensitive instruments, this added activity can noticeably affect the noise floor. One solution is to force the host application to close the communication port during the noise-sensitive acquisition phase and then reopen it for the data-transfer phase.

#### **PROTOCOL PARTICULARS**

My instruments always include a diagnostic ASCII protocol comprising simple two-character commands and heavy use of punctuation. Commands contain one or two alphabetic characters followed by an optional numeric argument and a semicolon, and spaces are ignored. For example: • To set the transmit pulse width to 50

• To set the transmit pulse width to 50 µsec, the host sends "PW 50;"

• If the instrument understands the command, it sends a confirmation: "PW 50!"

• If the command isn't in the instru-

- 0.4 Watts to 150 Watts Power Transformers

- 115V/26V-400/800 Hz Primary

- Secondary Voltages 2.5V to 300V

- Manufactured to MIL-PRF 27 Grade 5, Class S, (Class V, 155°C available)

- Surface Mount or Plug-In

- Smallest possible size

See Pico's full Catalog immediately www.picoelectronics.com

#### PICO Electronics, Inc

143 Sparks Ave., Pelham, NY 10803 Call Toll Free 800-431-1064 E Mail: info@picoelectronics.com FAX:914-738-8225

Delivery - Stock to one week INDUSTRIAL • COTS • MILITARY ment's vocabulary or if the argument is out of range, it returns "PW 50?"

If the host wants to read the current setting of the transmitter pulse width, it sends the command in lowercase: "pw;"

The instrument returns "pw50!"

This protocol is inappropriate for efficiently transferring large blocks of data, and usually gets supplemented or replaced as the host software is developed. Still, it allows you to control an instrument from any terminal emulator. I put the same protocol on the USB and asynchronous ports, with both ports always active, so I can use one for the main host interface and the other for a diagnostic port.

At the host end of the system chain, Changwook Min, a mobile-programming engineer at Massachusetts General Hospital's Center for Systems Biology, wrote the code to control the DMR-3 and analyze the returned data. He performed the initial development on an Apple Macintosh computer, using Objective-C under the Apple's Xcode 3.2.5 IDE (integrated device environment). He then ported the application to the iPhone 3G and iPad running iOS Version 4.2. Xcode has no native graphing or plotting framework, so Min used Apple's Core Plot.

#### **REVISION: NOT TO BE**

If I'd had a chance to clean up the design, I would turn the bottom three boards into one. I'd stick with the Delfino DSC, discard the CPLDs, and couple the PulSAR ADC directly to the DSC through the McBSP port. I'd either

Figure 5 Signals take paths in the DMR-3 as they traverse the design's various circuits.

replace the DDS chips with a dual part or, more daringly, use a single DDS for the transmitting and receiving chains. After all, we don't acquire data while transmitting, so there's no reason why one DDS couldn't do both functions.

I'd optimize the RF power amps for the actual power; we were unsure of the power budget when we performed the initial design and, therefore, went a little overboard. I would also design the receiver path with cost in mind, replacing the second VGA (variablegain amplifier) with something more appropriate.

Such a redesign will never happen, however. Once a concept is proven and the science is done, you either abandon the instrument or throw it "over the wall" to industry—to an engineering team that will undoubtedly start from scratch.EDN

#### ACKNOWLEDGMENT

The author would like to thank Hakho Lee and his talented team at the Massachusetts General Hospital Center for Systems Biology, especially physicist Dave Issadore and programmer Changwook Min. Thanks also to Keith Brown of Harvard SEAS for his NMR tutelage, and to Al Takeda for photographing the DMR-3 viscera.

#### REFERENCES

Reusch, William, "Nuclear Magnetic Resonance Spectroscopy," Michigan State University, http://bit.ly/lsPuCJ. Haun, Jered B: Cesar M Castro: Rui Wang; Vanessa M Peterson; Brett S Marinelli; Hakho Lee; and Ralph Weissleder, "Micro-NMR for Rapid Molecular Analysis of Human Tumor Samples," Science Translational Medicine, Volume 3, Issue 71, Feb 23, 2011, pg 71ra16, http://bit.ly/iRM95X. Issadore, David; Changwook Min; Monty Liong; Jaehoon Chung; Ralph Weissleder; and Hakho Lee, "Miniature magnetic resonance system for pointof-care diagnostics," Lab on a Chip, May 5, 2011, http://bit.ly/j7FlmL.

#### AUTHOR'S BIOGRAPHY

Jim MacArthur is the chief engineer at Harvard University's Electronic Instrument Design Laboratory. He has a bachelor's degree in electrical engineering from the Massachusetts Insti-

tute of Technology (Cambridge, MA).

Innovator of the Year Robert Dobkin and Tom Hack Linear Technology

Analog ICs EM773 energy-metering IC NXP Semiconductors

Application-Specific Standard Products VDAP1000 PowerSmart™ Display Panel Controller Integrated Device Technology

Development Kits, Reference Designs, and Single-Board Computers Tower System Freescale Semiconductor

#### **Digital ICs**

SmartFusion intelligent mixed-signal FPGAs Microsemi Corporation

EDA Tools and ASIC Technologies

PathFinder Apache Design Solutions

Human-Machine Interface Technology

mTouch metal-over-capacitive touch-sensing technology Microchip Technology Inc. Passive Components, Sensors, Indicators, and Interconnects MT9H004 image sensor

with DR-Pix technology Aptina

#### **Power ICs**

LT4180 virtual remote sense controller Linear Technology

#### **Power Supplies**

BSV-nano POL converter Bellnix America Inc.

#### Processors

Cortex-M4 processor ARM

#### Software

WEBENCH FPGA Power Architect National Semiconductor

#### Test and Measurement Systems and Boards

PXI and AXIe test portfolio Agilent Technologies

For more information on the *EDN* Innovation Awards, visit http://innovation.edn.com.

# EDA TOOLS PAVE PATH TO

#### BY MIKE DEMLER • TECHNICAL EDITOR

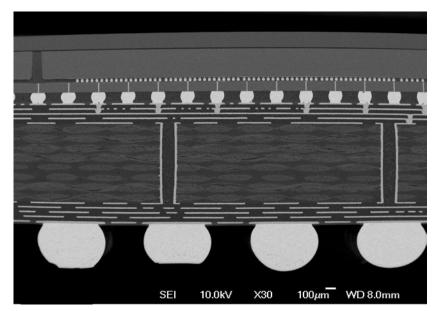

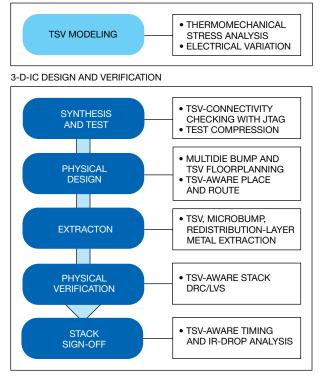

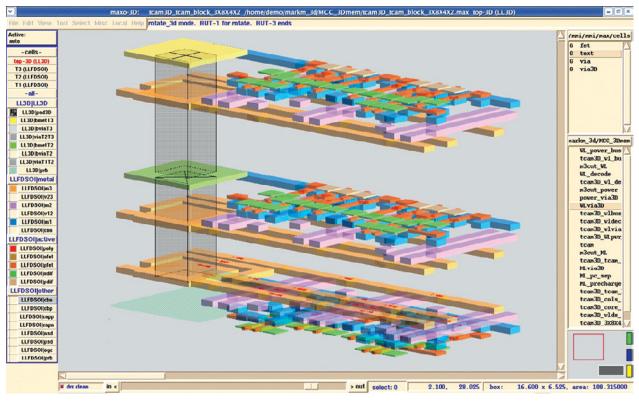

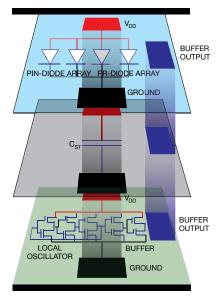

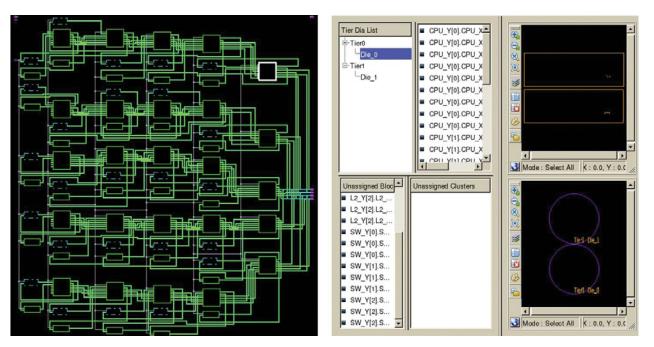

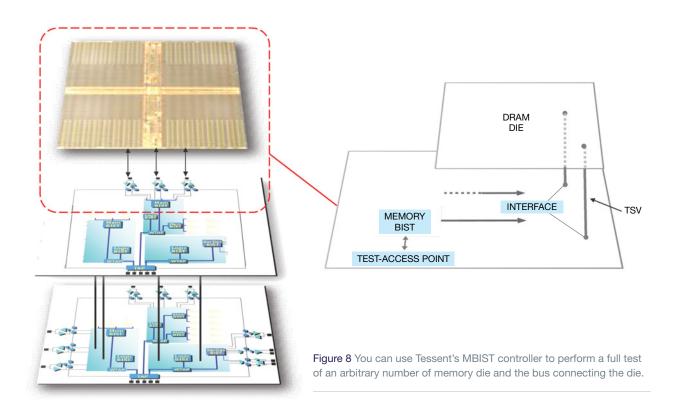

recent article (**Reference 1**) posed three questions regarding 3-D ICs: What are 3-D ICs, are they real, and what difference do they make? The answers to these questions may vary, but the semiconductor industry is increasingly add-ing a vertical—that is, stacked—alternative to traditional 2-D Moore's Law scaling (**Reference 2**).

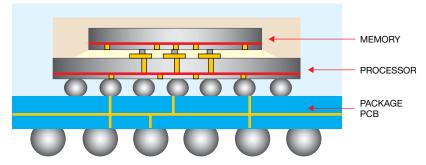

Reducing the length of interconnects between ICs can make a big difference in performance, power, and package size in mobile-system applications—major drivers for 3-D ICs. Combining a mobile-processor die with a separate memory chip is a natural development for a 3-D structure. For example, Samsung

Electronics recently introduced a 3-D IC, which the company stacks with a memory chip that connects using TSVs (through-silicon vias)—vertical, metallized holes in the silicon die that create connections on both the top and the bottom of a chip (**Figure 1**). TSV technology enables a wide I/O-memory interface, reducing power by as much as 75% versus other approaches as a result of the lower load capacitance of interconnect and I/O circuits.

Tezzaron Semiconductor, which specializes in memory products, 3-D-wafer processes, and TSV processes, stacks chips in three layers by using a waferbonding technique that employs copper supercontacts similar to the method the US Mint uses to make quarters in a copper-nickel-clad process. Tezzaron's Super-8051 microcontroller with stacked memory consumes 90% less power than a typical 8051 microcontroller because it has no off-chip I/O. It does not, however, allow manufacturers to probe wafers before bonding because probe marks can cause defects.

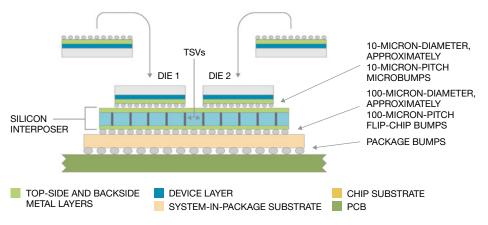

To mitigate some of the challenges of 3-D stacked ICs, many companies are taking an intermediate step— 2.5-D—to connect dice with a passive silicon interposer (Figure 2). Many industry participants, including Mentor Graphics Chief Executive Officer Walden Rhines, see the 2.5-D approach as providing a long transitional ramp to 3-D ICs (**Reference 3**). Rhines believes that 2.5-D approaches will be around longer than many people expect because the approach is more evolutionary than revolutionary.

Xilinx has also taken this approach in its new 2.5-D SSI (stacked-siliconinterconnect) FPGAs, including the Virtex-7 XC7V2000T, which integrates four FPGA dice with the equivalent of 2 million logic cells, 46,512 kbits of block RAM, 2160 DSP slices, and 36 10.3125-Gbps Xilinx GTX (gigabit-transceiverextension) transceivers (**Figure 3**). By stacking the dice on a passive silicon interposer, Xilinx enables more than 10,000 interconnects between the FPGAs. Showing again how 2.5and 3-D make a difference in power and performance, Xilinx achieved a better-than-two-orders-of-magnitude improvement in I/O bandwidth per watt with SSI versus other approaches, says Ivo Bolsens, Xilinx's chief technology officer.